亂抦揑岲婏怱偺尒抧偐傜丄惀旕偲傕棟桼傪岞奐偟偰捀偒偨偄撈憂媄弍亃

http://www.amd.com/epd/processors/4.32bitcont/13.lan4xxfam/22.lansc400/index.html

偐傜Elan400偺僨乕僞僔乕僩傪扵傞偲丄師偺傛偆側崁栚偑偁傞丅

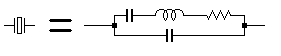

堦斒偵悈徎敪怳婍偼

偲偄偆夞楬偱慻傑傟傞偺偱丄偳偆傗傜ELAN偼偙偺僐儞僨儞僒偲偐掞峈傪撪憼偟偰偄傞傜偟偄丅

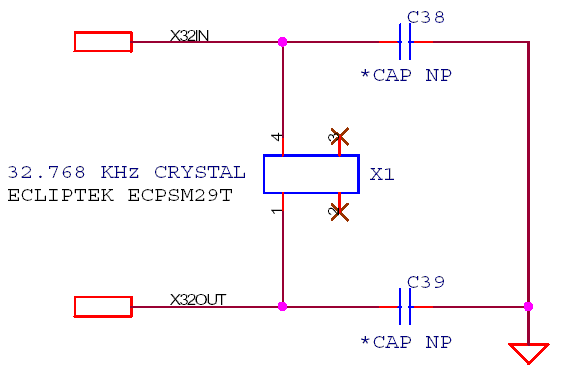

>The 32-kHz oscillator circuit is shown in Figure 6; the only external component required for operation is a 32.768-kHz crystal. The inverting amplifier (AMP) is integrated on-chip together with the feedback resistor and the load capacitors.

偲婰偝傟偰偄傞捠傝偱偁傞丅

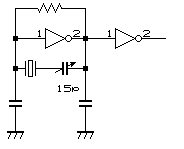

偲偙傠偱丄傾儗偱偁傞偑丄http://www.morphyplanning.co.jp/Products/MorphyOne/schematic_ver2_4.pdf丂偵岞奐偝傟偰偄傞偑

偲側偭偰偄傞丅

偙偙偱俀偮偺媈栤揰偑偁傞丅

(侾)丂偙偺C53偺15pF偺僷儔偺僐儞僨儞僒偼壗偱偁傠偆偐丠偙傟偱偼摍壙夞楬偑

偲側偭偰偟傑偆婥偑偡傞丅偙偺僐儞僨儞僒偺堄枴偼惀旕偲傕抦傝偨偄偲偙傠偱偁傞丅乮僋儘僢僋偺旝挷惍丠乯

2002/11/21捛婰丗

朸嫄戝摻柤宖帵斅偺彂偒崬傒偵傛傟偽丄敾柧偟偨條偱偡丅

乮偡傫傑偣傫丄堷梡偟傛偆偲巚偭偨傫偱偡偑丄慡懱揑偵岥挷偑傾儗側傫偱徣棯偝偣偰捀偒傑偡丅偡傫傑偣傫亜尒偮偗偰偔傟偨恖乯

--------------------------------------------------------------

http://morphy-ml.hp.infoseek.co.jp/ohpa/msg03243.html

[ohpa:3243] ELAN 宱尡幰偲偟偰

<XTAL晹>

丒偙偺傑傑偱偼帪寁惛搙偑弌側偄偲巚偄傑偡丅32KXTAL1僺儞偲僋儕僗僞儖係僺儞娫偵

丂捈楍偵15pF偺僙儔僐儞傪擖傟偨曽偑椙偄偱偟傚偆丅屻偱挷惍偡傞昁梫偑偁傝傑偡偑丅

--------------------------------------------------------------

偼偄丅偼偭偒傝偲32KXTAL1僺儞偲僋儕僗僞儖係僺儞娫偵乽捈楍偵乿偲傾僪僶僀僗偝傟偰傑偡偹丅

偙傟偼傑偀惓偟偔偰丄惛枾側敪怳婍傪嶌傞偲側傞偲

偭偰偄偆條偵丄悈徎偵捈楍偵僩儕儅僐儞僨儞僒傪捛壛偟偨夞楬偼傛偔尒傜傟傑偡丅

偲偄偆傢偗偱丄扨弮偵丄32KXTAL1僺儞偲僋儕僗僞儖係僺儞娫偭偰偄偆偺傪丄僋儕僗僞儖偺侾亅係僺儞娫丂偲撉傒娫堘偊偨偲巚傢傟傑偡丅

傑偀摍壙夞楬偭偰偄偆偲 丂偭偰偄偆偺傕偁傝傑偡偐傜丄堦奣偵娫堘偄偱偼側偔丄

丂偭偰偄偆偺傕偁傝傑偡偐傜丄堦奣偵娫堘偄偱偼側偔丄

暲楍偵擖傟偰偟傑偭偨15pF偼晧壸挷惍偩偲巚偊偽丄偙傟偱摦偐側偔側傞丄偲寛傔晅偗傜傟傞傕偺偱傕柍偄傫偱偡偑丄傾僪僶僀僗捠傝捈楍偵擖傟偨傎偆偑偄偄傛偆側婥傕偟傑偡丅

乮俀乯MC206乮乮Xtal)偺俀丆俁斣僺儞偺庢傝埖偄

僄僾僜儞僨僶僀僗偺僒僀僩偺帒椏丗

http://www.epsondevice.com/qd/products/suisyo_sindousi/MC-206/pdf/MC_206.pdf

偵傛傟偽

仈俀丄仈俁偼奜晹愙懕偟側偄偱偔偩偝偄丂偲彂偄偰偁傞偺偩偑丄忋婰夞楬恾偱偼GND偵棊偲偟偰偁傞傛偆偵尒偊傞偑丄傗偼傝奐偄偰偄傞僺儞偑僋儘僢僋嬤偔偵偁傞偲丄僆乕僾儞偵偡傞傛傝GND偵棊偲偟偰埨掕壔偝偣偨偄丄偲偄偆強偩傠偆偐丠

偙偺曈傕偳偺條偵峫偊偰偦偆偟偨偺偐抦傝偨偄偲偙傠偱偁傞丅

偪側傒偵杔偼Xtal傪娷傫偩夞楬偺愝寁偼偟偨偙偲偑側偄偑丄巇條彂偵NC偺僺儞偑偁偭偨偲偟偨傜丄偦偙偼偳偙偵傕宷偘側偄偺偑晛捠偩偲巚偆偺偱丄偙偺偁偨傝偼忋婰偺條偵僆乕僾儞偵偟偰偟傑偆晄埨掕惈傪婋湝偟偨儌僲偩偲偡傟偽戝塸抐偐傕偟傟側偄丅

2002/11/21捛婰

朸嫄戝宖帵斅傊偺彂偒崬傒偵傛傝傑偡偲

344 柤慜丗嶐擔偺Xtal巜揈偺偍偣偭偐偄 搳峞擔丗02/11/20

17:21 ID:???

>>338

偪側傒偵丄AMD偺儕僼傽儗儞僗偼丄偙偆側偭偰傑偡丅

偍傕偄偭偒傝丄XTAL偺俀丆俁偼×偟偰偁傝傑偡偹乮倵

妋偐偵丅乮徫乯丅

2002/11/23捛婰丗偙偙偺ELAN偵偮偄偰偄傞丄C38,C39偺僐儞僨儞僒偱偡偑

The crystal capacitor locations on the evaluation board are not populated and丂not necessary in a finished design. They were included for testing purposes only.

偲偄偆偙偲偱偡丅乮柍偄偺偑晛捠乯

朸宖帵斅傛傝夋憸傪捀偒傑偟偨丅

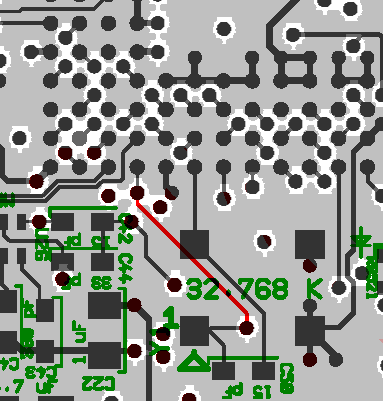

32.768偲昞婰偝傟偰偄傞偺偑丄偳偆傗傜悈徎偺傛偆偱偡丅塃懁偺忋壓俀僺儞偼偳偆傗傜俧俶俢偵棊偪偰偄傞傛偆偱偡丅

偱丄娞怱偺悈徎偲俠俹倀偺攝慄偱偡偑丄偆偅傓丅價傾偱懠憌傊堷偄偰傑偡偹偉丅傑偀宷偑偭偰傝傖偄偄傫側傜偄偄偐丅

朸嫄戝摻柤宖帵斅偵傛傟偽丄

734 柤慜丗偄偮偱傕偳偙偱傕柤柍偟偝傫 搳峞擔丗02/11/19

18:43 ID:???

偡偄傑偣傫丅偳慺恖側傫偱嫵偊偰梸偟偄偗偳

悈徎偭偰丄價傾捠偟偰丄懠偺憌偵愽偭偰偐傜丄傑偨價傾捠偟偰丄IC偵宷偖傎偆偑偄偄傫偱偡偐丠

傏偔側傫偐慺恖偩偐傜丄壗傕峫偊偢丄昞憌偩偗偱丄恀偭愭偵僋儘僢僋偲悈徎傪嵟抁偱宷偄偪傖偆傫偱偡偑丅

736 柤慜丗偄偮偱傕偳偙偱傕柤柍偟偝傫 搳峞擔丗02/11/19

18:46 ID:???

>>734

晛捠偦偆峫偊傞傛偹丅

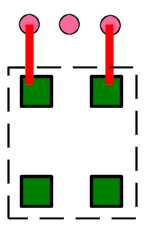

X'tal傕90°夞揮偡傞偲椉抂巕偑摨偠挿偝偵弌棃傞偨傔

峏偵偄偄姶偠丅

偩偦偆偱偡丅偪側傒偵儃僋傕慡偔摨堄偱偡丅

乮偙傫側姶偠丠乯

偙偺偁偨傝丄乽宷偑偭偰傝傖摦偔乿傕偺偐傕偟傟側偄偺偱丄愨懳僟儊偭偰傢偗偠傖偁傝傑偣傫偑丄

乽傢偞傢偞僷僞乕儞傪挿偔偟偰傑偱撪憌傪捠偟偡偺偵丄偳偆偄偆儊儕僢僩偑偁傞偺偐丄媄弍揑偵偼偲偰傕嫽枴偑偁傝傑偡乿

(2002.11.23夋憸偲偐捛壛)

偪側傒偵俠俹倀儃乕僪乮俉俵俫倸偩偗偳乯偺儕僼傽儗儞僗偵偼丄僋儘僢僋偲俠俹倀偺宷偓曽偵偮偄偰悇彠僷僞乕儞偑忔偭偰偄傞偺傕偁傞偔傜偄偱丄

悈徎偲俠俹倀偺攝慄偺偟偐偨偭偰偄偆偺偼丄恄宱傪巊偆傋偒売強偩偲偄偆偺偑巹尒偱偡丅

偙偺偁偨傝丄朸嫄戝摻柤宖帵斅偱偼丄

乮曇拲丗夋憸偺戝偒偝傪曄偊偝偣偰捀偒傑偟偨乯

乮曇拲丗夋憸偺戝偒偝傪曄偊偝偣偰捀偒傑偟偨乯偲偄偆偺偑懡悢堄尒偺傛偆偱偡偑丄

偲偄偆偙偲偱丄傑偀寢榑傪旔偗傞偲偟偰傕丄偦傫側姶偠偱偡

偮偄偱偵丄僋儘僢僋廃傝偠傖側偔偰丄僋儘僢僋壓偺攝慄偱偡偑

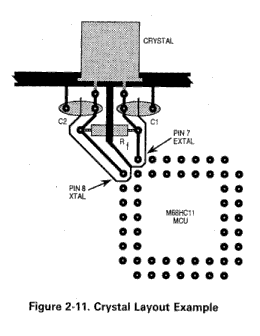

偲丄揹尮憌偼丄昞憌偺偡偖壓偺憌偵側偭偰偄傞丅傑偨丄僋儕僗僞儖偺寢慄偵娭偟偰偼

Board Layout Suggestions

The following suggestions

concern the ElanSC400 microcontroller evaluation

board layout strategy for

the 32-kHz oscillator, the PLLs, and the power supplies.

The goal is to minimize

noise and noise coupling associated with the way the board

is laid out. Special

care is needed to minimize

board leakages which can be fatal

to pins that

are sensitive to

leakage currents, such as the two crystal oscillator

pins,

乮偮傑傝丄悈徎偺僺儞偵娭偟偰丄嬌椡拲堄傪暐偄側偝偄丂偭偰偙偲丅乯

XTAl1 and XTAL2.

32-kHz Oscillator

Prudent board layout for the 32-kHz oscillator suggests

the following precautions:

The crystal capacitor locations on the

evaluation board are not populated and

not necessary in a finished design.

They were included for testing purposes only.

Route the area around the oscillator by hand.

Keep the two traces, XTAL1 and XTAL2, as short as possible.

乮偮傑傝丄悈徎偺攝慄偼丄嬌椡抁偔偟側偝偄丂偭偰偙偲丅乯

Keep all noisy signals (e.g., PLL filters and other

clocking signals) as far away

from XTAL1 and XTAL2 as possible. XTAL1

is much more

sensitive to noise

coupling than XTAL2.

乮摿偵丄XTAL侾偼丄偲偭偰傕僲僀僘偵僙儞僔僠僽両乯

乮棳愇偵偙偙偼庣傜傟偰偄偰丄MO25偵偍偄偰丄XTAL侾偲悈徎偺攝慄偼嵟抁偱偡両丅執偄両乯

Minimize parasitic

capacitance between XTAL1 and XTAL2; even a few

picofarads

can potentially cause the oscillation frequency to be off target.

乮XTAL侾偲XTAL俀偺娫偺婑惗梕検偼丄悢倫F偱傕丄廃攇悢偺嫸偄偑弌傞傛乯

偭偰彂偄偰偁傞傫偱偡偑偹偉

乮2002.11.24捛婰丗2ch揑東栿(徫)乯